校本教材——电子信息基础系列

# 电子信息专业英语 Protel 版

(第二版)

■陈涛 张林丽 主编

# 内容简介

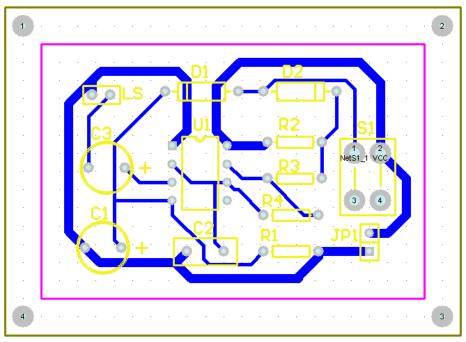

本书为电子信息专业的专业英语教材。 Protel 99 是应用最广泛的电子线路设计软件,使用简单、易于学习、功能强大。本书以Protel 99 英文版为基础,结合电子电路设计的特点,从实用角度出发,全面介绍了电路原理图的设计及印制电路板的设计方法。具体内容有 Prorel 99 基础、原理图设计环境的设置、电路原理图的设计、层次式原理图的设计、原理图元件的创建、电路板设计的基本知识、电路板设计环境设置、电路板规划和网络表的载入、印制电路板的设计、元件封装的创建、各种报表文件的生成及设计成果的输出,仿真等。全书内容翔实、层次分明、图文并茂、实例丰富,便于读者阅读和自学。本书面向高等院校电子信息类及相关专业学生,可作为电子信息专业英语教材,也可供电子线路设计工作者参考阅读。

第二版在先前版本的基础上,添加了词汇列表,以及实训环 节的参考内容,供各位读者参考。

# **Contents**

| Unit | 1    | Inc | rease your PCB Design Productivity With Protel 99 SE | 1   |

|------|------|-----|------------------------------------------------------|-----|

| Unit | 2    | Des | sign Explorer                                        | 4   |

| Unit | 3    | Hov | v to Start                                           | 8   |

| Unit | 4    | Wo  | rking with design objects                            | .13 |

| Unit | 5    | Wo  | rking in schematic documents                         | .18 |

|      | Part | 1   | Schematic electrical design objects                  | .18 |

|      | Part | 2   | Schematic drawing objects                            | .22 |

|      | Part | 3   | Schematic design directives                          | .26 |

|      | Part | 5   | Setting schematic workspace preferences              | .29 |

|      | Part | 6   | Setting schematic document options                   | .31 |

|      | Part | 7   | Using schematic sheet templates                      | .34 |

|      | Part | 8   | Managing schematic components                        | .35 |

|      | Part | 9   | Editing schematic component libraries                | .39 |

|      | Part | 10  | Repositioning design objects on a schematic          | .42 |

|      | Part | 11  | Wiring up a schematic                                | .44 |

|      | Part | 12  | Workspace editing techniques                         | 51  |

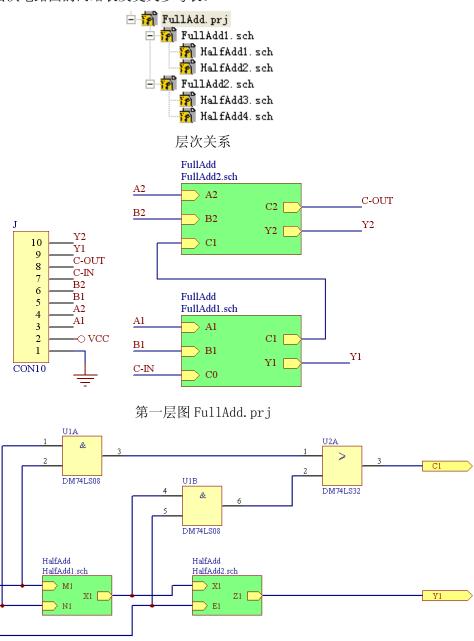

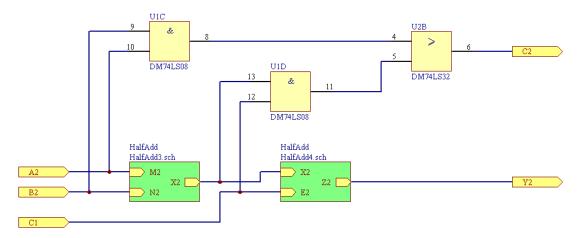

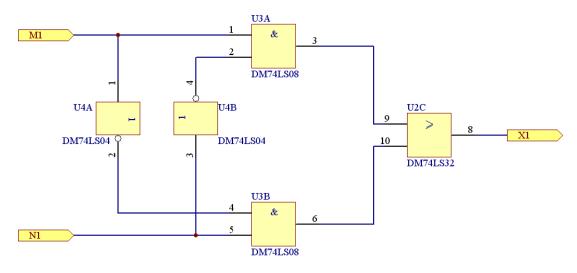

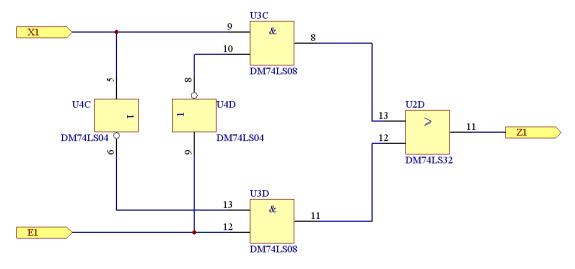

|      | Part | 13  | Creating projects with multiple schematic sheets     | .54 |

|      | Part | 14  | Schematic design verification - the ERC              | .58 |

| Unit | 6    | Wo  | rking in PCB documents                               | 62  |

|      | Part | 1 l | PCB design objects                                   | 62  |

|      | Part | 2 1 | PCB design layers                                    | 67  |

|      | Part | 3 1 | Defining a new PCB                                   | 69  |

|      | Part | 4 l | PCB connectivity                                     | 87  |

|      | Part | 5 I | Managing PCB components                              | .93 |

|      | Part | 6 I | Using PCB design rules1                              | .08 |

|      | Part | 7   | Navigating a PCB document                            | 13  |

|      | Part | 8   | Manually routing a PCB                               | 16  |

| Par    | t 9  | Autorouting a PCB                               | 7  |

|--------|------|-------------------------------------------------|----|

| Par    | t 10 | Verifying the PCB design                        | :0 |

| Par    | t 11 | 3 dimensional PCB visualization                 | :3 |

| Par    | t 12 | Printing to a windows printing device           | :5 |

| Unit 7 | Syn  | achronizing schematic & PCB documents           | :7 |

| Unit 8 | Wor  | king with simulations                           | 3  |

| Par    | t 1  | Selecting simulation-ready schematic components | 5  |

| Par    | rt 2 | Creating digital simulation components          | 9  |

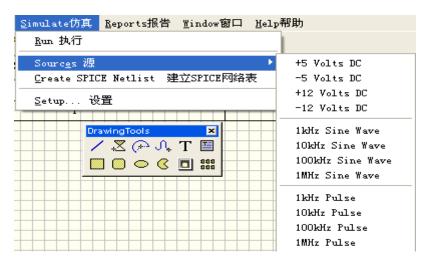

| Par    | t 3  | Adding simulation sources to a schematic        | -1 |

| Par    | t 4  | Identifying simulation circuit nodes            | -1 |

| Par    | t 5  | Running simulation analyses                     | .2 |

| 实训一    |      | 14                                              | 4  |

| 实训二    |      | 15                                              | 1  |

| 实训三    |      | 15                                              | 5  |

| 实训四    |      |                                                 | 9  |

| 实训五    |      | 16                                              | i4 |

| 实训六    |      | 17                                              | '4 |

| 词汇表    | (部分  | r)18                                            | 1  |

# Unit 1 Increase your PCB Design Productivity With Protel 99 SE

Welcome to the Protel 99 SE Designer, your comprehensive guide to exploring and using the new and enhanced features included in Protel 99 SE. The information in this book will help you get the most from Protel 99 SE's advanced board design features, and complements the comprehensive information provided in this book.

Protel 99 SE is the version of Protel's integrated board-level design system for the Windows NT/98/95 operating system. It builds on the foundation of Protel's unique Design Explorer platform, introduced with the relrase of Protel 99, by adding a host of new and enhanced features aimed at streamlining the board design process.

Protel 99 SE's Design Explorer integration platform has been optimized to give fast application and design document opening, more responsive performance and more efficient memory usage. You now have a choive of design data storage methods – save your integrated design in a single Access database, or as stand – alone files and folders using the simplicity of the Windows File System. With either storage method you have available the full power and convenience of Protel 99 SE's design

management and integration features.

From design entry through to manufacturing output creation, Protel 99 SE gives you greater design flexibility and power. Capture your design faster and more accurately with Protel 99 SE's enhanced schematic editor, that now features direct on-sheet text editing, sheet-by-sheet and positional annotation, automatic component class creation based on source schematic sheets, plus a host of time-saving editing and interface enhancements.

Create your board from 32 signal layers, 16 internal plane layers, and 16 mechanical layers, with fully-definable layer stackup and drill layer pairing. With enhanced power plane connectivity, new design rules and rule scopes, and import/export of design rule sets, Protel 99 SE's PCB editor gives you unparalleled versatility in board design definition.

New and enhanced interactive component placement tools will slash

design layout time. Protel 99 SE supports on-board graphical creation and editing of placement rooms, dynamic real-time optimization of connection lines during component moves, and the ability to group components for fast placement of component blocks.

New and enhanced interactive component placement tools will slash design layout time. Protel 99 SE supports on-board graphical creation and editing of placement rooms, dynamic real-time optimization of connection lines during component moves, and the ability to group components for fast placement of component blocks.

New PCB design features in Protel 99 SE include a powerful PCB print management system, an advanced 3D PCB renderer and viewer, and an invaluable CAM Manager that gives you "one click" output generation.

The above enhancements and features are just a taste of the many ways in which Protel 99 SE makes your desktop a more productive board design environment. Please explore this supplement and see just how much easier design can be with Protel 99 SE.

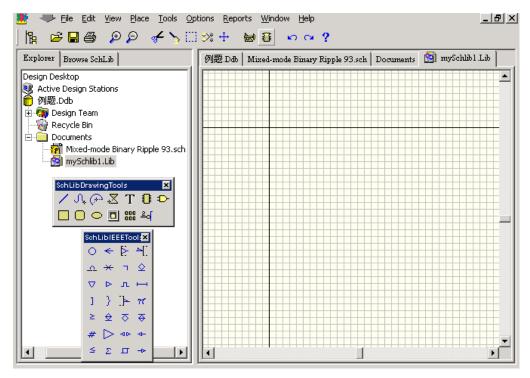

# **Unit 2** Design Explorer

The Design Explorer is the name given to the Protel 99 SE design environment. When you select Protel 99 from the Windows Start menu, the Design Explorer opens. The Design Explorer is the interface to your designs, and the various design tools that you use to create your designs.

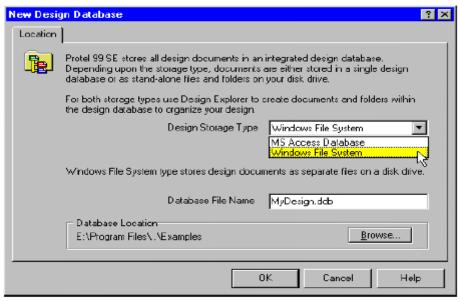

#### **Windows File System Storage Option**

Protel 99 SE includes a new document storage option that stores design documents directly on a diskdrive. The New Design Database dialog includes a new Design Storage Type option, where you specify if the design documents will be stored in a single integrated Microsoft Access database, or if they will be stored directly on a disk drive.

Select the document storage type when you create a new design

If the Storage Type is set to MS Access Database then all design documents are stored in a single database. If the Storage Type is set to Windows File System then all design documents are stored directly on the disk drive in the location specified at the bottom of the dialog.

Regardless of the storage system that is chosen, the way you work in the Design Explorer is exactly the same. If your design uses the Windows File System Storage Type you still open the design first – then open the schematic, PCB, or other design documents.

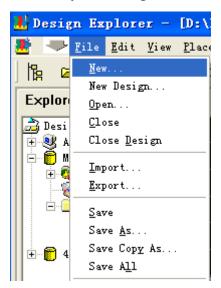

New documents are created in the same way for both storage types, select *File* » *New* to create a new document. Note that you can not move documents into a Windows File System database with the Windows File Explorer, they must be imported into a database before they can be opened. You can import a number of files by importing a folder, or by dragging from the Windows File Explorer directly into an open design.

Designs that use the Windows File System storage do not support any of the DesignTeam features, such as document access control. Other design integration features, like synchronization and background document opening when printing and netlisting, are supported.

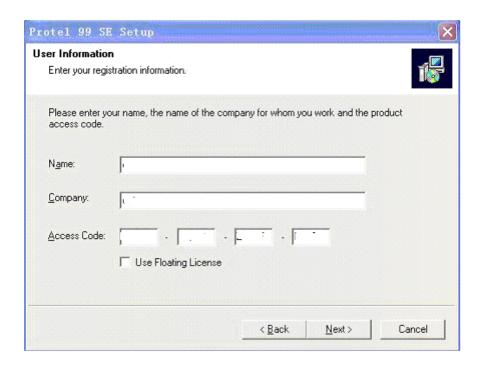

#### **Floating Licenses**

Protel 99 SE supports floating licenses. This system allows you to install Protel 99 SE on as many PCs as you like – Protel 99 SE automatically monitors how many copies are running and displays a warning message when there are too many copies running at the same time.

If your network includes PCs that must have a single-user license permanently allocated disable the Broadcast and Receive Floating Access Codes options at the bottom Security Locks dialog.

# **Unit 3** How to Start

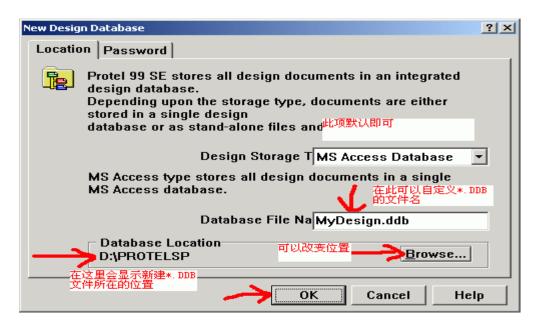

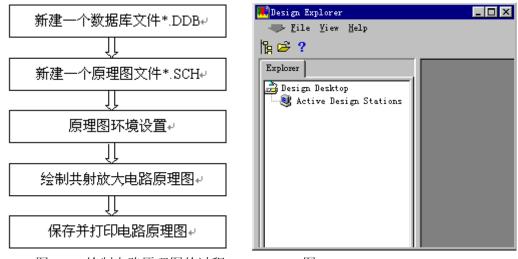

#### Creating a new design

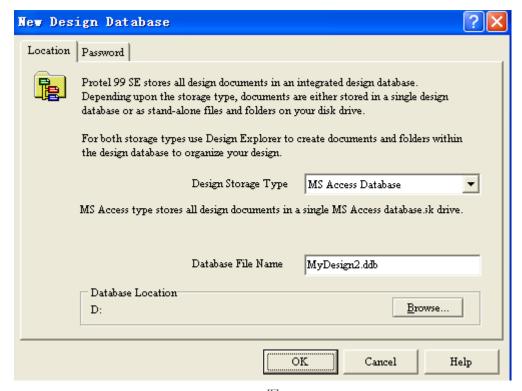

To create a new Design Database select File ?New Design from the menus. The New Design Database dialog will pop up. Complete the following steps:

- 1. Select the Storage Type

- 2. Enter the Database name

- 3. Set the location as required

If you would like to password-protect the Design Database now, click on the Password tab and enter the password. This password is assigned to the default user name Admin. You can password-protect a Design Database at any time, by going to the Members folder and entering a password for the Admin member. To unprotect a Database remove the password from the Admin member. Note that you can only password-protect a design database whose storage type is MS Access database.

Once the new design database is created an icon for it will appear in the navigation tree of the Design Explorer, and its corresponding design window will open in the work area.

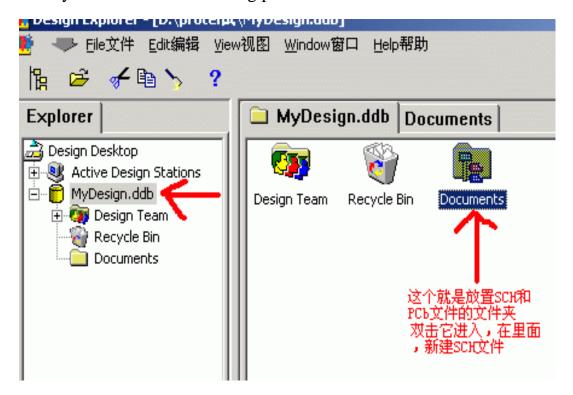

Then you will see the following picture:

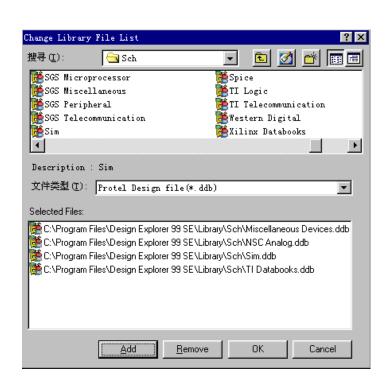

#### Adding a .SCH file

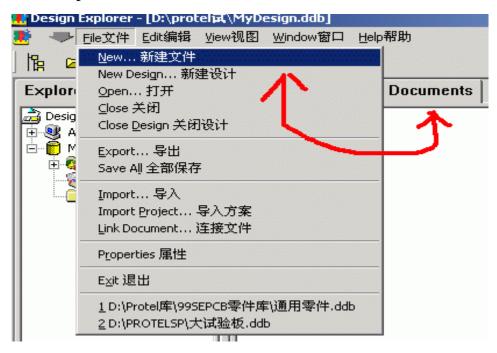

The first step is:

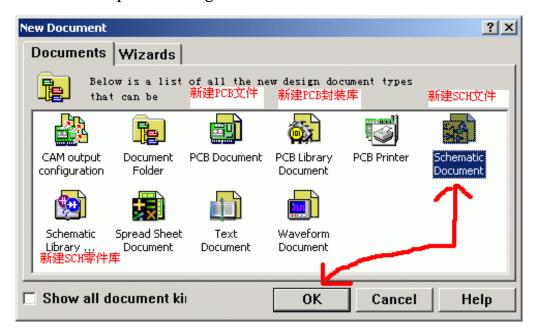

The second step is selecting the Schematic Document file:

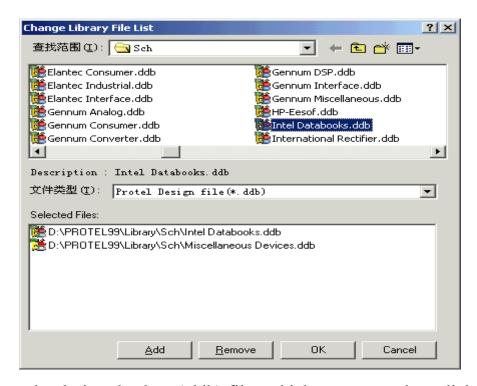

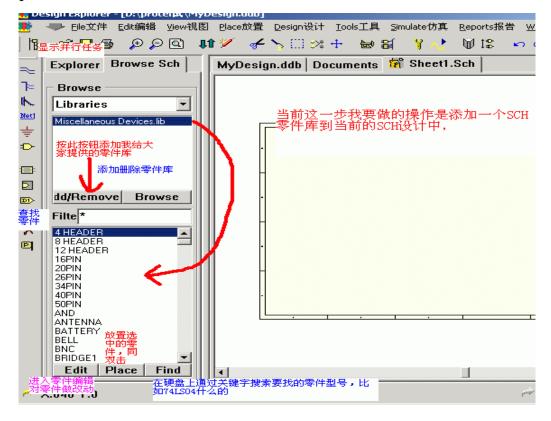

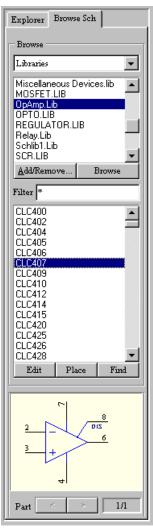

The third step ,click the tab of the Browse Sch, you will see the following picture.

Select the design database(.ddb) files which you want, then click the Add button to add other design databases to the list. You can then browse within the design database that is currently selected. When you locate the required document click on it to select it, then click on the OK button.

# Working with the Navigation Tree

The Design Explorer Design Manager panel provides a navigation tree with a Windows Explorer-like navigation panel that shows a hierarchical view of the documents and folders contained within an open design database. Folders are shown as folder icons in the tree, and documents are marked with an appropriate icon. A small box next to a tree branch indicates that the document or folder contains other documents or folders.

# Unit 4 Working with design objects

Design objects are the building blocks of both schematic and PCB documents. You construct schematic and PCB designs by placing and arranging design objects on a schematic sheet or PCB layout document. Everything you use to construct you design is a design object, including components, tracks, wires, text annotations, etc.

The following topics detail the manipulation of design objects in Protel, and apply to both schematic and PCB designs.

## Placing design objects in documents

The method for placing objects is similar for both schematic and PCB documents. The basic placement steps are outlined below.

- 1. Select the object that you want to place? You can do this by selecting an object from the Place menu or by clicking on one of buttons from the various placement toolbars. For components and footprints, you can also click the Place button in the Panel when browsing libraries.

- 2. When an object is selected for placement, the cursor will change to a crosshair, indicating that you are in editing mode, and, if relevant, the

object will appear "floating" on the cursor.

- 3. Press the TAB key to edit the properties of the object before placing it. This will open the property dialog for the particular object, allowing you to change various options. Once you have finished setting the properties, close the dialog to return to placement mode.

- 4. Position the cursor and left-click or press ENTER to place the object. For complex objects such as wires, tracks, polygons, etc. you must continue the position and click procedure to place all vertices of the object. Note: If autopanning is active, you can move around the document by simply moving the cursor past the edge of the editing window in the direction that you wish to go.

- 5. After placing an object you will remain in placement mode (indicated by the crosshair cursor), allowing you to place another object of the same type immediately.

- 6. To end placement mode, right-click or press the ESC key (in some cases, such as placing a polygon, you may need to do this twice; once to finish placing the object and once to exit placement mode). When you exit placement mode, the cursor will return its default shape.

#### Editing design objects in documents

Any design objects you have placed in a schematic or PCB document

can be modified in a variety of ways. Objects can be moved around within the document, and cut, copied and pasted within and between documents. Also, you can edit the properties of objects to change their colors, layers, designator, net assignment, etc. With some objects, such as polyline shapes (tracks, wires, polygons, fills, etc), you can graphically change the shape of the object after it has been placed.

The topics below detail the general techniques for editing objects within PCB and schematic documents.

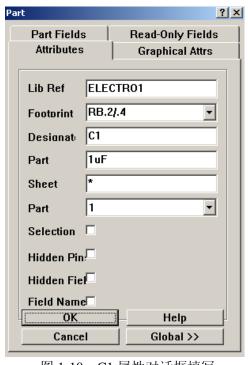

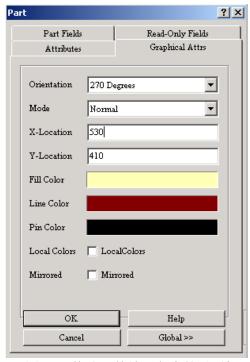

#### Changing the properties of a design object

All objects in schematic or PCB documents have a defined set of properties associated with them. These properties can include position, color, layer, selection status, etc. To view or edit the properties of any object, open its associated Properties dialog in one of the following ways:

- 1. When an object is "floating" on the cursor during the placement procedure, press the TAB key to open its properties dialog.

- 2.For any object placed in a document, double-click the object to open its properties dialog directly.

- 3.Select Edit → Change from the menus to enter the object change mode. Click on the object that you want to edit. Right-click or press ESC to exit object change mode.

#### Selecting design objects for editing

Before performing any editing action that operates on multiple design objects, such as aligning objects in schematic or PCB documents, you must first select the objects you wish to work with.

There are several ways to select objects:

- 1. Hold the SHIFT key down and left-click on an object.

- 2.Click-and-drag to draw a selection box around objects.

- 3.From a schematic or PCB document, select Edit ?Select from the menus to open the Selection submenu [shortcut S]. Use the item on this menu to make group selections in a number of ways.

Selected objects are outlined in the selection color (default is bright yellow). To change the default selection color, from a schematic or PCB document select Tools ?Preferences from the menus.

In Protel, selection of objects is cumulative: selected objects remain selected until you manually deselect them. Selecting additional objects DOES NOT deselect any objects currently selected.

To deselect an object:

- 1. Hold the SHIFT key down and left-click on a selected object.

- 2.From a schematic or PCB document, select Edit ?DeSelect from the menus to open the Deselection submenu [shortcut X]. Use the item on this menu to deselect groups of selected objects in a number of ways.

#### Setting the match attributes for global editing

When performing a global edit on an object type, the Attributes to Match By fields in the global editing portion of the object's properties dialog define the set of objects that the global edit will apply to.

If the property is a text field, you can use the "?" and "\*" wildcard symbols to define the text in this field to match by. A ? defines any single character, and a \* defines any group of characters. For example, to match all schematic components with designators of the form U1, U2, etc., you would enter the string U\* in the Designator Attributes to Match By field.

Non-text fields will include a dropdown list in their corresponding Attributes to Match By fields, from which you can select Any, Same or Different to match objects which have any value, the same value or a different value respectively in these fields.

To define the set of objects you wish to apply the global edit to, set the appropriate Attributes to Match By fields to define the matching criteria. These fields are logically "ANDed" together to form the match criteria.

# **Unit 5** Working in schematic documents

## Part 1 Schematic electrical design objects

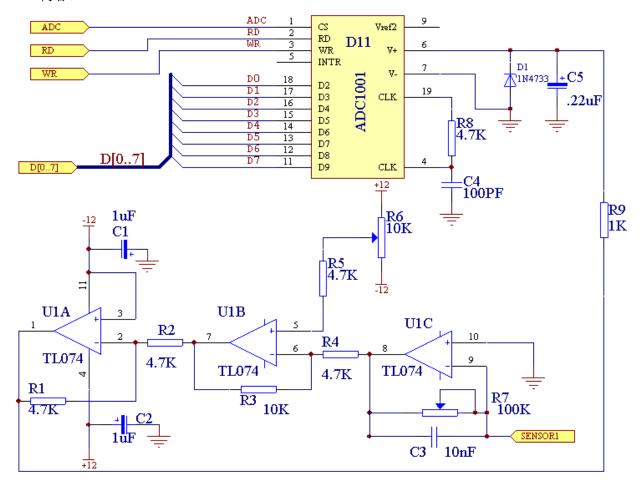

A schematic is a diagrammatic representation of an electronic circuit, and schematic capture is the process of capturing a design as a schematic in a computer-aided design environment. A computer-based schematic is more than a simple drawing of the circuit. It also contains information about the connectivity of the circuit and the parts that make up the circuit.

In Protel, the basic workspace for capturing a schematic is called a schematic sheet. Electrical, drawing and directive objects are placed on a schematic sheet to design the circuit and produce working schematic drawings. A complete circuit design can use just a single sheet, or it can comprise a number of electrically linked sheets. Protel allows you to create complex hierarchical and modular designs by linking any number of sheets to form a complete project.

Schematic electrical design objects define the physical circuit you are capturing. These objects are used to create a netlist from the schematic, which is then used to transfer circuit and connection information between

design tools.

#### **Bus (Schematic electrical design object)**

Toolbar: WiringTools → For Menu: Place → Bus

Description: A bus is a polyline object that represents a multi-wire connection. A bus can be assigned to multiple nets using a Net Label of the form "D[0..7]" or "D[7..0]", indicating that the nets D0 to D7 are carried by the bus. Use a Bus Entry object to connect to, or branch from a bus.

To place: Once in bus placement mode, left-click or press ENTER to anchor the starting point for the bus, then position the mouse and left-click or press ENTER to anchor a series of vertex points that define the shape of the bus. When you have finished drawing the bus, right-click or press ESC. Repeat the previous steps to draw another bus object, or right-click or press ESC to exit bus placement mode.

Press the TAB key during placement to edit the object's properties.

Graphical editing: When a bus object is in focus, the following editing handles are available. Click handles A to reposition the end points of the bus. Click handle B to move a bus vertex. The end points will remain anchored. Click A B near the center of a bus segment to grab that segment and reposition it.

#### **Bus entry (Schematic electrical design object)**

Toolbar: Wiring Tools Toolbar: Wiring Tools

or Menu: Place →Bus entry

Use a bus entry to connect to or branch from a bus object. Place the bus entry so that it touches the target bus object. The bus entry then forms a "stub" that you can use as a signal wiring point.

#### Part (Schematic electrical design object)

Toolbar: WiringTools

Toolbar: WiringTools

A part is a schematic symbol that represents an electronic device, such as a resistor, switch, opamp, IC, etc. Parts are stored within components in schematic component libraries. A component within a library represents a physical device. Each component contains one or more parts.

#### **Junction (Schematic electrical design object)**

Toolbar: Wiring Tools → Tor Menu: Place → Junction

A junction forms an electrical connection where two or more wires cross. A junction is automatically inserted when a wire starts or terminates anywhere along the length of another wire. When a wire crosses other wires, no junction is inserted. If you want to create a connection between crossed wires, place a junction at the crossing point.

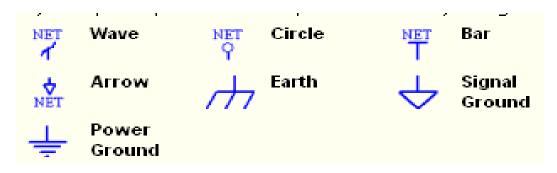

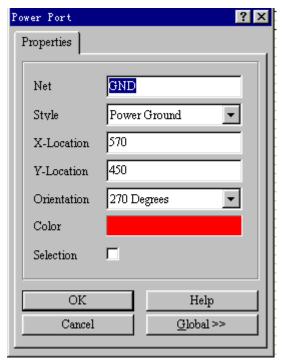

## Power port (Schematic electrical design object)

A power port is a special schematic object that lets you easily define a power or ground net. Seven graphical styles of power port are available, and can be set by editing the object's properties.

# Wire (Schematic electrical design object)

A wire is a polyline object that forms an electrical connection between points on a schematic, and is analogous to a physical wire.

#### **Net label (Schematic electrical design object)**

A net label assigns a particular net name to an electrical object. When a netlist is generated, default names will be given to each net in the schematic. Manually placing a net label on your schematic defines the name of the net to which it is attached.

#### Port (Schematic electrical design object)

A port is used to make an electrical connection between one schematic sheet and another sheet or sheet symbol in a design using multiple sheets. The name of the port, set in the port properties dialog (press TAB during placement, or double-click on a placed port to open this dialog), defines the connection (i.e. a port on a schematic sheet connects to ports or sheet entries with the same name on other sheets in the project).

Part 2 Schematic drawing objects

#### **Annotation (Schematic drawing object)**

Menu: Place → Annotation

Description:An annotation allows you to place a single line of free text on a schematic sheet. For more extensive, multi-line text, use the Text Frame object. Annotations are also used to reference special schematic information strings in schematic templates.

#### **Text frame (Schematic drawing object)**

Description: A text frame is used to define an area on a schematic to contain textual information. The frame is a resizable rectangular area that can contain multiple lines of text, and can automatically wrap text to keep it within the bounds of the frame. For simple one line text annotations, use the Annotation object.

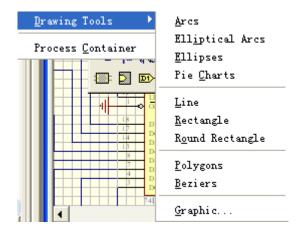

#### **Arc (Schematic drawing object)**

Toolbar: none Menu: Place→Drawing Tools→Arcs

Description: Draws a circular arc on the current schematic sheet.

#### Elliptical arc (Schematic drawing object)

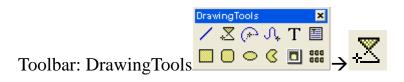

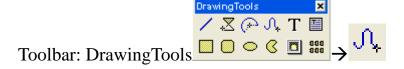

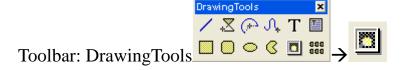

Toolbar: DrawingTools

Toolbar: DrawingTools

Menu: Place→Drawing Tools →Elliptical Arcs

Description: Draws an elliptical arc on the current schematic sheet

#### Ellipse (Schematic drawing object)

Menu: Place → Drawing Tools → Ellipses

Description: Draws an ellipse on the current schematic sheet.

#### Pie chart (Schematic drawing object)

Menu: Place→Drawing Tools→Pie Charts

Description: Draws a circular sector or "pie chart" object on the current schematic sheet.

#### **Line (Schematic drawing object)**

Menu: Place → Drawing Tools → Lines

Description: Draws a multi-segment line on the current schematic sheet.

#### **Rectangle (Schematic drawing object)**

Menu: Place→Drawing Tools→Rectangle

Description: Draws a rectangle on the current schematic sheet.

# Round rectangle (Schematic drawing object)

Menu: Place → Drawing Tools → Round Rectangle

Description: Draws a rectangle with rounded corners on the current schematic sheet.

#### **Polygon (Schematic drawing object)**

Menu: Place → Drawing Tools → Polygons [P D P]

Description: Draws a polygon shape on the current schematic sheet.

#### **Bezier curve (Schematic drawing object)**

Menu: Place → Drawing Tools → Beziers

Description: A Bezier curve allows you to draw free-form curved lines on a schematic sheet. The curve is defined by a series of vertex points that "pull" the line into a curved shape.

#### **Graphic (Schematic drawing object)**

Menu: Place → Drawing Tools → Graphic

Description: This inserts a graphic file as an object in the current schematic sheet. The following file types are supported:1.Bitmaps (.bmp, .dib, .rle). 2.JPEGs (.jpg). 3.Windows Metafiles (.wmf)

# Part 3 Schematic design directives

Schematic design directives attach additional design information to particular circuit nets. This information is not used in the schematic, but is incorporated into the netlist and can be used by other design tools, such as the autorouter or simulation engine.

No ERC (Schematic design directive)

Toolbar: WiringTools

WringTools

Net

N

Menu: Place → Directives → No ERC

Description: Placing this directive on a node in the circuit suppresses

any report warnings and Error Markers that may be generated for the

node when running an Electrical Rules Check (ERC). Use this directive

to deliberately prevent ERC checking of certain parts of a circuit that you

know will generate a warning (such as unfinished connections) while

checking the rest of the circuit.

**Probe (Schematic design directive)**

Toolbar: none

Menu: Place → Directives → Probe

Description: A Probe is a special marker which is placed on the

worksheet to identify nodes for digital simulation during netlist

generation.

**Test vector index (Schematic design directive)**

Toolbar: none

27

Menu: Place → Directives → Test Vector Index

Description: Test Vectors are special symbols used to identify a node

with a simulation test vector. The test vectors are referred to by a column

number, which indicates the column of the test vector file to use when the

simulation is run. Note: This directive is currently not used internally by

Protel.

**Stimulus (Schematic design directive)**

Toolbar: none

Menu: Place → Directives → Stimulus

Description: A Stimulus is a special symbol which is used to identify

a node or net to be stimulated when the digital simulation is run.

**PCB** layout (Schematic design directive)

Toolbar: none

Menu: Place→Directives→PCB Layout

Description: Allows you to assign PCB layout information to a net in

the schematic. When a PCB is created from the schematic, the

information in the PCB Layout directive is used to create relevant PCB

design rules.

28

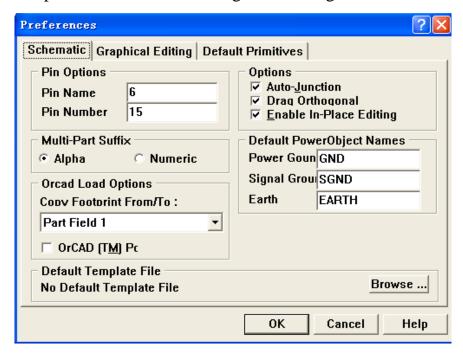

#### Part 5 Setting schematic workspace preferences

Schematic preferences affect the schematic editing environment and are save as part of the Protel environment. These preferences apply to all schematic sheets.

To set the schematic environment preferences you must have a schematic sheet as the active document. Select Tools→Preferences from the menu to open the Preferences dialog. This dialog has three tabs:

Schematic tab:In this tab you control the appearance of the labeling of part pins, enable the Drag Orthogonal and Auto-Junctioning options, and set the default template used when creating new schematic documents.

Graphical Editing tab: In this tab you set various options controlling the editing environment, autopanning and undo/redo stack.

Default Primitives tab: In this tab you control the default properties and behavior of the design objects used to create schematics.

To set the default template used to create new schematic sheets, select Tools > Preferences from the menu when a schematic sheet is active. In the resulting Preferences dialog, make the Schematic tab active. In the Default Template File field, enter the path and name of a valid schematic template (schematic template files have a .DOT extension), or press the Browse button to search for a file.

When you are performing an editing action in a schematic sheet, moving the cursor to the edge of the work window will automatically pan the sheet in the appropriate direction, allowing you to navigate the sheet without having to use the scroll bars.

To control the speed of autopanning, or to turn off autopanning completely, select Tools→Preferences from the menu when a schematic sheet is active. In the resulting Preferences dialog, make the Graphical Editing tab active. Set the Autopan Options fields to change the autopanning behavior.

1.Style: Sets the way the sheet is scrolled during autopanning. Select an option from the dropdown list. Choosing Autopan off disables autopanning.

2.Speed: Sets the panning speed. This is independent of sheet size and sheet contents. Hold the SHIFT key to autopan at a higher speed.

For help on setting individual controls in the Preferences dialog, use the "What's This" help available when the dialog is open. The visible grid is used as an aid for visually aligning objects on a schematic.

To change the way the visible grid is drawn, select Tools→Preferences from the menu when a schematic sheet is active. In the resulting Preferences dialog, make the Graphical Editing tab active.

The lines used to draw the visible grid can be draw either solid or dotted. To select a line type, change the option in the Visible Grid field.

To set a color for the visible grid, click the color sample box in the Grid Color field and choose a color from the color selection dialog.

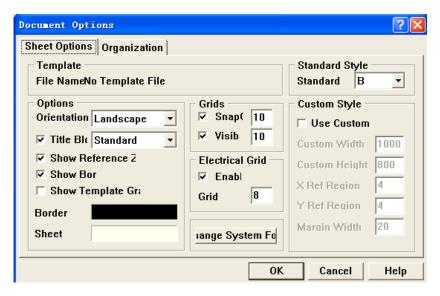

# Part 6 Setting schematic document options

Schematic document options are properties of individual schematic sheets. These options are stored with the schematic sheet. Changing a document option only affects the currently active sheet.

To set the options for the active schematic sheet, select Design

→Options from the menus to open the Document Options dialog. This dialog has two tabs:

Sheet Options tab: In this tab you configure the sheet size and orientation, border style, title block, grid ranges, background color, and system font.

- 1. To select a custom sheet size, enable the Use Custom Style option and set the desired values in the Custom Style fields.

- 2. Select the desired orientation in the Orientation field to set the schematic sheet orientation

- 3. You can automatically include a border and grid area around the edge of a schematic sheet. A border is a line around the edge of the drawing area. A grid area, or reference zone, draws a set of grid reference marks around the edge of the schematic inside the border area. To show or hide the border line, check or uncheck the Show Border option. To show or hide the reference zones, check or uncheck the Show Reference Zones option.

- 4. When performing any editing action in a schematic, the cursor movement is restricted to points that lie on the schematic snap

- grid. This grid can be set independently from the visible grid. To enable or disable the snap grid, check or uncheck the SnapOn option. To set the size of the snap grid, enter a value in the SnapOn field.

- 5. The schematic electrical grid is a special grid designed to assist you in wiring up your schematic. The electrical grid defines a range around electrical objects within which the cursor is "captured" by the object, overriding the current snap grid. Wires, part pins, etc, are all affected by the electrical grid. With the electrical grid turned on, as you wire up your schematic, the cursor will automatically "find" electrical hot spots, making it easier to connect to electrical objects. To enable or disable the electrical grid, check or uncheck the Electrical Grid Enable option. To set the size or capture range of the electrical grid, enter a value in the Grid Range field.

- 6. The schematic visible grid is used purely as an aid for visually aligning objects on a schematic. The setting of this grid has no affect on the cursor movement during editing. To enable or disable the visible grid, check or uncheck the Visible option. To set the size of the snap grid, enter a value in the Visible field.

- 7. All text on a schematic sheet that is not part of a design object is rendered in the default font for that sheet. Items which use

this default font include: border text, system title blocks, pin names, pin numbers, ports, power ports and sheet entries. Press the Change System Font button on the to select a default font.

Organization tab: In this tab you enter company and design information to be used in the Title Block for the sheet.

# Part 7 Using schematic sheet templates

he sheet border, title block and included graphics make up what is referred to as the sheet template. Protel 99 SE comes supplied with a number of sheet templates, one for each size of sheet available. Schematic templates are stored in the schematic Templates folder in the Templates. Ddb design database. This design database is in the \Design Explorer\System folder in the Protel installation directory on your hard disk.

To assign a template to a schematic sheet, from the schematic select Design →Template→Set Template File Name from the menus. The Select dialog will appear. The drop-down list at the top of the dialog includes all design databases that are currently open in the Design Explorer. To add the Templates.Ddb database click on the Add button, browse to the \Design Explorer\System folder and double click on the Templates.ddb file. You can now browse within this design database to the Schematic

Templates folder, and select the required template.

When you click OK the Set Template dialog will appear, click OK to apply this template to just the active schematic, or Apply to All to update all schematics in this project. It will not affect other schematics in the design database that are not part of this project.

User defined sheet templates can be created. They are created in the same way you create a normal schematic sheet. After adding all the objects to the sheet that you want to appear in the template, select File → Save Copy As from the menus. In the resulting dialog, set the Format to either Schematic template binary or Schematic template ascii. You must give the template a name ending with a .DOT extension. Click OK to save the template file in the design database.

As well as including custom title blocks and graphics, sheet templates can include special strings to automatically add document text when printing or plotting.

# **Part 8 Managing schematic components**

Schematic component descriptions are stored in schematic libraries, which can be stored within a design database or as external files named with a .LIB extension. The default schematic libraries supplied with Protel 99 SE are stored within a series of design databases located in the

Design Explorer 99 SE\Library\Sch folder in your Protel installation directory.

New libraries are constantly being developed by the Protel Library Development Center. Visit the PLDC on the web at www.protel.com for the latest downloadable libraries.

Each schematic component then consists of one or more parts, which represent the functional devices contained within the component. For example, a 74LS00 contains four parts (AND gates), a capacitor has one part, and a relay can be made up of a coil part and a contact part.

Components are created and modified in the schematic library editor, an independent document editor that includes tools for managing and editing libraries. You can open a schematic sheet the schematic library editor simultaneously, with special features to link between sheet and library operations. For example, you can move directly from a part symbol on the sheet, to editing its component information inside the source library.

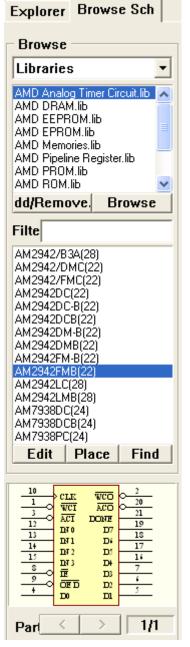

# Making schematic libraries available for use

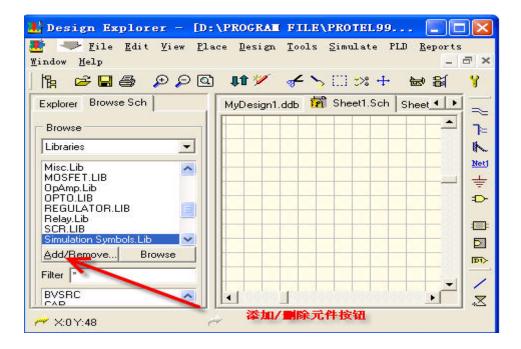

To access the components in the schematic libraries, the libraries must first be added to the list of available libraries in the schematic sheet editor.

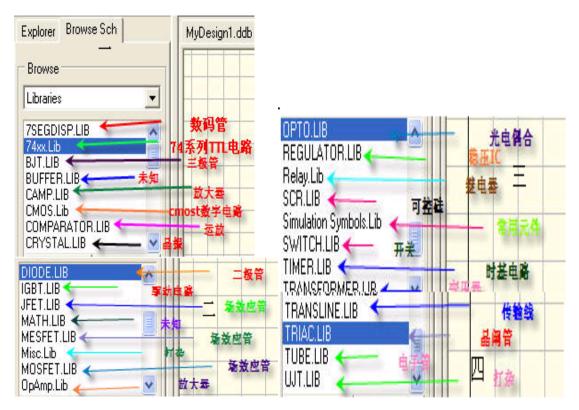

To view a list of currently available libraries, set the Browse scope to Libraries in the schematic panel. A list of currently loaded libraries will be shown. Click on a library name in the list to show a list of all components it contains in the lower list box.

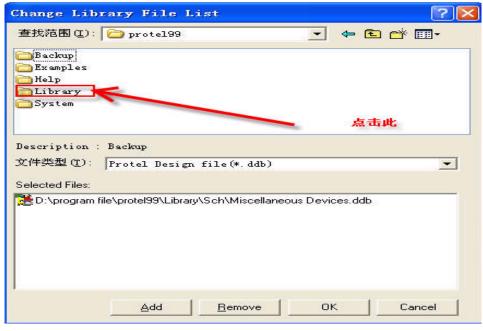

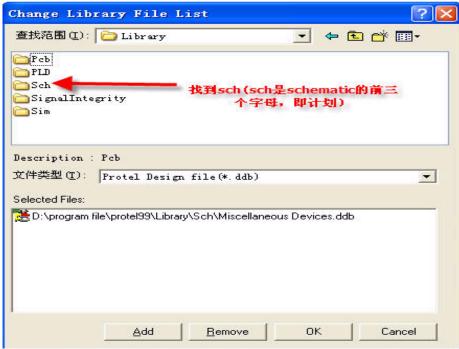

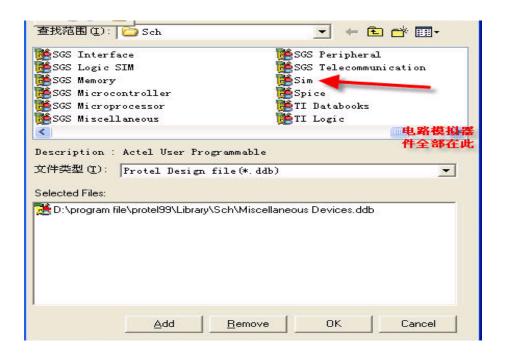

To add libraries to the available libraries list, click the Add/Remove button on the panel, or select Design→Add/Remove Library from the menus. This opens the Change Library List dialog, where libraries can be added and removed from the Current File List. The only

limit on the number of libraries that can be added is the memory available in your computer. Once libraries have been added, parts from those libraries can be placed on the sheet.

The default schematic libraries supplied with Protel 99 SE are stored within a series of design databases (.DDB files) located in the Design Explorer 99 SE\Library\Sch folder in your Protel installation directory.

Each design database may include a number of individual schematic libraries. Selecting a design database adds all the libraries it contains to the available libraries list.

### Finding components within schematic libraries

Protel 99 SE includes the ability to search all schematic libraries in a predefined path for a component. To find a component in a library, when a schematic sheet is active press the Find button on the schematic editor panel, or select Tools → Find Component to pop up the Find Schematic Component dialog.

Following are some tips on searching for components:

- 1. If possible, search by Library Reference as it is much faster. Also the way you describe a component may not be the way it has been described in the library.

- 2. Include the \* wildcard before and after the library reference, as different manufacturers use different prefix and suffixes.

- 3. If your search produces no results check that the Path is correctly specified. Also, try searching for a component that you know is in a library to check that everything is set correctly.

- 4. Use the Add to Library List button once you locate the correct component to add the library to the available libraries list.

#### **Browing component libraries**

You can browse for schematic components in the schematic panel, using the MiniViewer that appears at the bottom of the panel when the Browse mode is set to Libraries. You can also browse schematic component libraries in the Browse Components dialog (Design→Browse Library).

## Placing parts from schematic libraries

To view a list of currently available components, from the schematic document set the Browse scope to Libraries in the schematic panel. A list of currently loaded libraries will be shown in the top list box. Click on a library name in the list to show a list of all components it contains in the lower list box.

Select a component in the lower list box of the schematic panel and press the Place button.

# Part 9 Editing schematic component libraries

Schematic component descriptions are stored in schematic libraries, which can be stored within or linked to a design database, or stored as external files named with a .LIB extension. The default schematic libraries supplied with Protel 99 SE are stored within a series of design

databases located in the Design Explorer 99 SE\Library\Sch folder in your Protel installation directory.

Schematic libraries are managed using the schematic library editor, which is used to create and modify the components symbols and descriptions contained within schematic libraries.

To be able to edit a schematic library in Protel 99 SE, it must be stored in or linked to a Protel design database.

To edit a schematic library, use the Design Explorer to open the design database containing the library or library link. Design databases that contain schematic libraries can be manipulated as you would any other design database.

Simply use the Design Explorer to open a stored or linked schematic library as a document within the design database. Schematic library documents are automatically opened with the schematic library editor.

## Creating a new schematic library

To create a new schematic library, first open or create a design database in which to store the library.

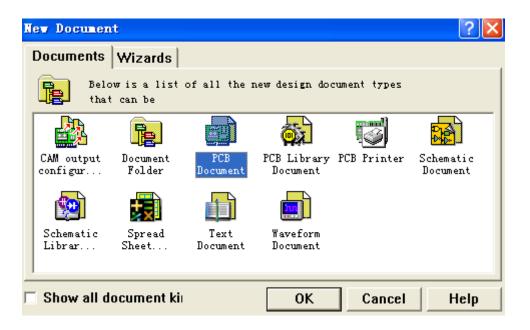

To create a new schematic library, from within a design database select File→New, and double click on the SchLib icon in the New Document dialog. A new empty schematic library document will be created in the current folder of the design database. To open the library,

double-click on its icon in the design window, or click on its icon in the navigation tree.

As a library is a set of components, it can not exist without at least one component. When you create a new library, an empty component sheet (called Component\_1) is also created within the library. To rename Component\_1 with a name of your choice, open the library, select Component\_1 from the list in the schematic library editor panel, and select Tools ?Rename Component from the menus.

#### **Editing components in schematic libraries**

Within each schematic library are a set of components. Each component within the library consists of one or more parts. The component represents the physical device, and the parts represent the functional devices it contains. For example, a discrete resistor component would have just one part, whereas a resistor network might have eight parts, each representing a single resistor within the physical resistor network package.

The partitioning of components into parts is entirely up to you as the designer. You may wish to draw the coil of a relay as one part and the contacts as another, or it might be more appropriate to draw the whole relay as one part. A four pin connector could be drawn as one part, or it could be drawn as four parts. Each part of a component is drawn on a

separate sheet within in the schematic library editor.

As well being able to have more than one part, each part can have up to three graphical representations, or modes; Normal, De-

Morgan and IEEE. Each mode is drawn on a separate sheet. The preferred mode is selected when the part is placed on the schematic sheet, with the default being normal. Only the Normal mode must be created, the other two are optional.

# Part 10 Repositioning design objects on a schematic

In Protel schematic documents there are two main ways of repositioning design objects: objects can be moved or dragged.

- 1. Moving an object changes its position on the sheet without maintaining connectivity. Any connect wires are not moved with the object and any connections will be broken.

- 2. Dragging an object change its position on the sheet whilst maintaining connectivity. Any connected wires are moved with the object being dragged so that the connectivity of the schematic is maintained.

Moving and dragging can be performed on single objects, or on selected groups of objects.

To move a single object or selection, from the schematic select Edit > Move > Move or Edit > Move > Move Selection from the menus to enter move mode. The cursor will change to a crosshair. Left-click on an object (or any object in a selection) to "pick up" the object. Move the cursor to reposition the object(s) and left-click or press ENTER to place the object. Right-click or press ESC to exit move mode.

To drag a single object or selection, repeat the above procedure, but select Edit→Move →Drag or Edit →Move →Drag Selection from the menus.

To align selected objects on both axes, from the schematic select Edit ?Align ?Align to open the Align Objects dialog [shortcut A A]. Select the desired vertical and horizontal alignment from the option buttons and click OK to have all selected objects moved to the chosen horizontal alignments. Enable the Move Primitives to Grid option to constrain alignment to the nearest grid point.

The following single-axis alignments are available from the Edit

Align submenu or via shortcut keys:

Align Left CTRL+L

Align Right CTRL+R

Center Horizontal CTRL+H

Distribute Horizontally CTRL+SHIFT+H

Align Top CTRL+T

Align Bottom CTRL+B

Center Vertical CTRL+V

Distribute Vertically CTRL+SHIFT+V

# Part 11 Wiring up a schematic

Wiring up a schematic is the process of placing wires, buses ports and net labels on your schematic to define the connectivity of the circuit. The following topics discuss wiring up a single schematic sheet. See the Creating projects with multiple schematic sheets topic in the Links section below for information on connectivity in multi-sheet designs.

## Overview of connectivity in schematics sheets

Connectivity is the ability to recognize the physical links between objects inside a schematic sheet and to associate logical connections that exist between various sheets in a multi-sheet design. Connectivity is also used to anchor certain objects together. For example, you can drag connected electrical items (parts, buses, wires, ports, etc.) without breaking existing connections. More importantly, connectivity allows the schematic to generate netlists and perform electrical rule checks.

Connectivity is derived from the placement of certain electrical objects in the sheet and from the placement of net identifiers. However,

not all electrical objects use placement to define connective behavior. Some objects use their geometry to establish physical connectivity. Other objects include logical connectivity in their behavior.

Electrical objects are connected when their electrical "hot spots" are touching. When the electrical grid is enabled (Design → Options) the cursor will jump to the nearest hot spot and change into a "dot" shape, indicating a valid electrical connection can be made.

Special cases of connectivity are:

Wire to Wire: Wires whose ends touch at any angle, butt end-to-end or have co-linear (overlapping) terminations are deemed to be connected. Co-linear wires that terminate elsewhere on the sheet are not deemed to be connected. Wires that cross or terminate perpendicularly are not deemed to be connected unless a junction is placed at their intersection.

*Net Label to Wire*: Net labels associate a wire with single net. To achieve this association, the net label must be placed on the same grid point as the wire, either vertically or horizontally. Labels can only be placed on horizontal or vertical lines or at line vertices.

Wire to Bus: Buses are graphical representations of grouped signals, and do not have any special connective properties for netlisting. Although buses display hot spots when wiring and maintain connections during drags, they do not simulate electrical connections. Wires are graphically connected to buses using bus entry symbols. Net labels must be used to

indicate logical connectivity on either side of the bus connection.

Net Label to Bus: Buses are graphical entities and do not provide physical connectivity for netlisting. Logical connectivity for buses can be assigned by placing a net label on the bus. Generally, this net label will include all bus signals, e.g. HA[0..19] represents nets named HA0, HA1, HA2, etc. to HA19. Buses and bus entries do not highlight when the Edit »Select » Net process launcher is used.

Wire to Pin: Pins that touch the ends of wires at any angle are deemed to be connected. Pins that intersect perpendicular wires must be connected by placing a junction at that location. Junctions will be automatically inserted where wires cross pins perpendicularly when this option is active (Tools »Preferences menu item).

*Pin to Object:* Pins connect directly to other pins, wires, net labels, sheet entries or ports. Hidden pins can be assigned directly to nets in the Schematic Library Editor. Unhidden pins can also connect directly to other sheets, when that sheet is named in the part's Sheet Path field.

Wire to Port: A Wire touching the end of a port is deemed to be connected.

Pin to Pin: Pins are deemed to be connected if they are in contact at any angle.

Bus to Object: Buses are graphical representations of grouped nets only and have no special physical properties for netlisting. Logical

connectivity (use of net identifier, e.g. net label and port) is used in these cases to indicate connections on either side of a bus. Note however, if a bus is connecting to a port the bus line must end on the end of the port.

Wire to Sheet Entry: A Wire touching the end of a sheet entry is deemed to be connected.

*No ERC:* No ERC objects are deemed to be connected to pins or wires if they are in contact.

Two other special classes of electrical objects are provided. Directives: used to indicate; simulation points, unconnected pins (No ERC) and PCB layout properties on individual nets. Net identifiers: used to indicate electrical connections that are not physically wired together, eg. connections that continue from one schematic sheet to another in a multi-sheet design.

The process of placing electrical objects in the sheet is often referred to as wiring. This is because the connectivity features allow you to work with electrical objects as though you were physically hooking-up the circuit.

Net identifier objects support connections that are not physically joined by wires. These objects include: net labels that identify common nets on a sheet (or globally, across multiple sheets if you specify); ports that identify net connections between two sheets; sheet entries that identify net connections into a sub-sheet (referenced by a sheet symbol);

and power ports which are special symbols placed to represent a global power (or another user-specified) net.

Hidden pins on parts are a special fifth type of net identifier that function similarly to power ports. Hidden pins connect to all other hidden pins with the same name and connect to a net of the same name, if present. If "unhidden" these pins are not deemed to be connected and must be manually wired to be included in a netlist.

### Schematic guided wiring and auto-junctioning

Protel's schematic editor includes two features to help you place wires to electrically connect schematic objects

Guides Wiring: Schematics have a definable electrical grid that makes it easy to make electrical connections between objects. As you are placing a wire, when the wire falls within the electrical grid range of another electrical object, the cursor will snap to the fixed object and a Hot Spot (highlight circle) will appear. The Hot Spot guides you to where a valid connection can be made and automatically snaps the cursor to electrical connection points. It is recommended that you set the electrical grid to be set slightly smaller than the current snap grid, or it becomes difficult to position electrical objects one snap grid apart.

Auto-junctioning: The schematic auto-junctioning feature automatically places an electrical junction when one wire is terminated

(ends) on the body of another wire (in a "T" junction), or when a wire connects orthogonally to a pin or power port. This allows you to easily create electrical connections at junction points without the need to manually define the connection. Wires that cross away from their end points do not have a junction is inserted.

The auto-junction feature is enabled of disabled in the Schematic tab of the schematic Preferences dialog (from a schematic select Tools → Preferences).

## **Setting the schematic auto wire mode options**

When placing wires or buses in a schematic, a special auto wiring mode is available to automatically route wires and buses between points on the schematic.

When the auto wiring mode is active during wire or bus placement, press the TAB key to open the Point To Point Router Options dialog, which allows you to set the auto wiring options. The following options are available:

- 1. Clearance: Defines the minimum clearance between the wire and other objects on the sheet.

- 2. Time Out After (s): Sets the maximum time in seconds that the autowirer will try to calculate a path. If it cannot find a routing path within this time, it will stop and no wire will be placed.

3. Avoid cutting wires: The setting of the slider determines how hard the autowirer will try to avoid cutting crossing existing wires.

### Connecting schematic objects using net identifiers

In connectivity terms, a net defines electrically connected points in a circuit. By placing a wire between two nodes in a schematic, you effectively assign the two points to the same net. In a schematic, Protel internally assigns a unique name to each net in the circuit, but you can manually define net names to create connectivity between nodes on the schematic.

To manually assign a net name (or net identifier) to a point in your schematic, place a Net Label on that point. The net name is the name given to the Net Label.

If you assign the same net name two or more points on a schematic, these points are effectively connected electrically. You do not need to manually connect them using a wire.

The diagram (left) shows two electrically equivalent circuits. The top

shows two resistors connected in parallel using wires to

make the connections. The bottom shows two resistors

connected in parallel using net labels to define the

location of the connections of the connections.

A typical use of connections using net identifiers is

connecting to power nets. When you place a power port on a schematic it defines a net which has a net name equivalent to the power object's name (VCC, GND, etc.). You can then place net labels on any schematic circuit nodes which have the same net name as the power port to automatically connect these nodes. You do not need to physically wire the nodes to the power port.

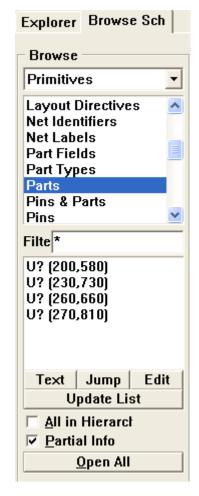

# Part 12 Workspace editing techniques

The schematic editor includes a number of features to make the design process more productive. These include:

## 1. Jumping around the workspace

To move quickly around the current schematic sheet select Edit > Jump from the schematic menus to open the Jump submenu.

## 2. Browsing with the panel

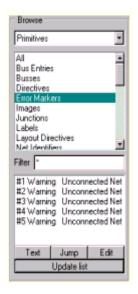

When a schematic document is active, the schematic editor panel can be used to browse through and locate the various objects on the current sheet, or the entire schematic project. Select Primitives in the pull-down list, then select the type of objects you wish to browse. A list of all objects of the selected type will appear in the list window.

You can filter this list by including a text mask (using the \* and ? wildcard characters) in the Filter field.

Select an object in the list and then:

- Click Jump to jump to the selected object, centering it in the design window.

- Click Text to jump to the selected object and edit its text field, if applicable.

- Click Edit to jump to the selected object and edit its properties.

- Click Update List to refresh the browse list.

Enable the Whole Project option to include

objects from all connected schematic sheets. Disable this option to limit the browse list to the active sheet.

Enable the Partial Info option to show only the names of the objects in the object list. Disable this option to show full details of the objects in the list window.

## 3. Morphing, or inheriting properties

Protel 99 SE's schematic editor has a powerful feature for copying the properties of one object into a second object of the same type. You can use this feature whenever you have an object floating on the cursor before placing it.

### 4. Finding and replacing text

Protel 99 SE allows you to find and replace text anywhere on a single schematic sheet, or across a multi-sheet project.

To find text, select Edit→Find Text from the menus.

To find and replace text, select the Edit→Replace Text from the menus.

## 5. Pasting arrays of objects

When a schematic object is on the schematic clipboard, it can be pasted into the schematic as an vertical or horizontal object array.

To do this select Edit→Paste Array from the schematic menu to open the Setup Paste Array dialog. In this dialog, the following options can be set:

Item count - the number of copies of the clipboard object(s) to paste.

Text increment - an integer defining the designator number increment for each Part object that is pasted.

Horizontal spacing - the horizontal spacing distance to the right between each pasted array object. If set to 0, pasted objects are in a vertical line.

Vertical spacing - the vertical spacing distance above each pasted array object. If set to 0, pasted objects are in a horizontal line.

Once you have set the options in the Setup Paste Array dialog, click OK to close it. Position the cursor where you want to insert the array and left-click or press ENTER to past the objects.

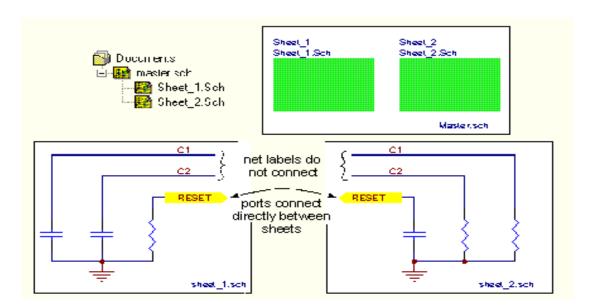

# Part 13 Creating projects with multiple schematic sheets

Protel 99 SE supports single sheet, multiple sheet and fully hierarchical schematic designs, including complex hierarchy, where multiple instances of a single sheet can be used in a project. There is no limit on the number of sheets that you can have in a design.

Multiple sheet projects support large or complex designs that cannot be served by a single sheet. Even when the design is not particularly complex, there can be advantages in organizing the project across multiple sheets. For example, the design may include various modular elements. Maintaining these modules as individual files allows several engineers to work on different parts of the design at the same time.

The relationship between sheets in a multi-sheet design is formed by a special symbol called a sheet symbol, which provides a graphical representation of subsheets in the design. Sheet symbols contain ports that represent links on the source schematic. Placing a sheet symbol on a schematic links that schematic to the sheet represented by the sheet symbol.

Before creating a multi-sheet schematic design, it is important that you understand how net identifiers are treated across the design, and the

different hierarchy models that can be used to electrically link net identifiers in multiple sheets. This will affect the way you name nets, power ports, etc. in the different sheets of a multi-sheet design.

## Linking schematic sheets using sheet symbols

Protel's schematic editor includes features to "automate" the process of creating and linking multi-sheet projects. When you start a multi-sheet project you adopt either a "top down" or "bottom up" approach to the design, or a mixture of both.

Top-down design involves defining the functional blocks of your circuit as sheet symbols on a master schematic, and then creating the schematics. If you adopt this approach, you can select Tools ?Create Sheet From Symbol from the schematic menus to automatically create the schematic subsheets based on the sheet symbols you have created. You will be prompted to select a sheet symbol. After clicking on a sheet symbol a new schematic sheet will open with the correct file name. The new sub-sheet will include ports to match each of the sheet entries on the sheet symbol you selected.

Bottom-Up Design involves creating the various schematics as independent circuits, then creating sheet symbols based on these schematics, then linking these sheet symbols on a master sheet to create

the final design. If you adopt this approach, select *Tools »Create Symbol From Sheet* from the schematic menus (the intended parent sheet must be the active sheet). The Choose Document to Place dialog will open with a list of all schematic sheets available in the same folder as the active sheet. Select the sheet you would like to base your sheet symbol on. You will then be asked if you want to Reverse Input/Output Directions. After you answer this (see below), you will be presented with a sheet symbol floating on the cursor. This sheet symbol will have sheet entries to match each of the ports on the selected subsheet.

Each of the ports on the sub-sheet has an I/O type. Say one of the ports has an I/O type of output. If you respond "yes" to the Reverse Input/Output Directions question then the sheet entry that matches this port will have an I/O type of input (the I/O direction has been reversed) and will be positioned on the left of the sheet symbol. If you respond "no" to the Reverse Input/Output Directions question then the sheet entry that matches this port will have an I/O type of output and will be positioned on the right of the sheet symbol.

This is called a "flat" design as all the sub-sheets are on the same level in the project hierarchy. The top sheet includes the sheet symbols for all the sub-sheets, but not any wiring or circuitry. In this model all the inter-sheet connection are made globally through ports, where ports of the same name are connected throughout the project. Note that the net names

in the two sub-sheets are local, meaning that the net name connects only within each sheet, not to other sheets in the project.

Management of large designs with this model can be awkward because it is difficult to trace a net from one sheet to another.

To use this model for multi-sheet schematic designs, set the Net Identifier Scope to Ports Only Global when performing an ERC, running a simulation, creating a netlist, compiling a schematic-based PLD, or synchronizing between schematic and PCB documents.

This model is referred to as complex hierarchy. In this model the same sheet symbol can be placed more than once in a project, either by being placed more than once on a single sheet, or by being placed on multiple sheets. This model fits projects which are highly modular. For example, a stereo amplifier, where left and right channels are identical circuits.

Complex hierarchy is used during the schematic capture phase. When

you are performing any electrical analysis on this type of multi-sheet design you must first "flatten" the design, converting it from complex to simple. From the schematic, select Tools→Complex to Simple to flatten the design. Each child sheet that is used more than once will be copied and renamed. You must also re-annotate the design to assign a unique designator to each part.

To use this model for multi-sheet schematic designs, set the Net Identifier Scope to Sheet Symbols / Port Connections, when performing an ERC, running a simulation, creating a netlist, compiling a schematic-based PLD, or synchronizing between schematic and PCB documents, after first converting the design from complex to simple.

# Part 14 Schematic design verification - the ERC

Design verification is the process of ensuring that the schematic capture process has produced an accurate "snap shot" of your design, from which a valid netlist can be created. In Protel's schematic editor this is done using the Electrical Rule Checker (ERC). This process examines the schematic for both electrical inconsistencies, such as an output pin connected to an output pin, and drafting inconsistencies, such as unconnected net labels or duplicate designators.

From a schematic document, select Tools ?ERC from the menus to

open the Setup Electrical Rule Check dialog. This is used to set-up and execute the Electrical Rule Check.

Running the ERC produces two results. First, a text report is generated, listing the electrical and logical violations either for the active sheet, or the entire project. Secondly, error markers are placed on the sheets at the site of each ERC violation as an aid in tracking and correcting reported problems.

There may be points in the design which you know will be flagged as ERC errors or warnings, which you do not want to be flagged. To suppress these, place a No ERC schematic directive objects at each point (Place→Directive →No ERC).

## **Browsing ERC errors on a schematic sheet**

After you have run an ERC on a schematic, any warnings or errors are shown as Error Marker objects on the schematic. You can easily identify all ERC errors in a schematic by using the schematic panel to browse through the Error Markers.

In the panel, set the Browse scope to Primitives and select Error Markers from the top list box. A list

of all error markers will appear in the bottom list box. Select an error in the list and press the Jump button to have the error marker presented in the center of the active window.

Note that a description of the error condition appears on the Status Bar, alleviating the need to switch back and forth to the error report. Pressing the Text button in the Component Browser will pop up a dialog which can also be used to examine the description of the error condition.

## **Typical causes of schematic ERC errors**

Errors found when performing an Electrical Rules Check (Tools > ERC) on a schematic will typically be due to the one or more of the following conditions:

- Drafting errors wires overlapping pins, lines being used instead of wires, the design being wired with the snap grid off so the wire ends don't touch the pin ends or wires / busses finishing under a port instead of touching the end of the port.

- Syntax errors net identifiers with spelling mistakes or busses incorrectly labeled.

- Component errors component pins placed the wrong way around on the component or pins with an inappropriate Electrical Type.

- Design errors a design condition that the ERC detects as an error, such as two output pins connected.

### Printing and plotting a schematic

Protel 99 SE includes support for a wide variety of hard copy options for schematic sheets. Virtually any device that is supported by Windows can be used to print or plot your schematic drawings.

Schematic printing and pen-plotting are handled similarly to other Windows applications. Windows manages the printing (or plotting) process and provides a range of raster and PostScript printer drivers and vector plotter drivers. These range from 9 pin dot matrix printers and multi-pen plotters, to high-resolution raster imagesetters.

To setup to print or plot from the active schematic or schematic library, select the File→Setup Printer menu item. This will open the Schematic Printer Setup dialog, allowing you to choose a printer and set up the output options.

To start the print process, click the Print button in the Schematic Printer Setup dialog, or from a schematic select File→Print from the menus.

# **Unit 6 Working in PCB documents**

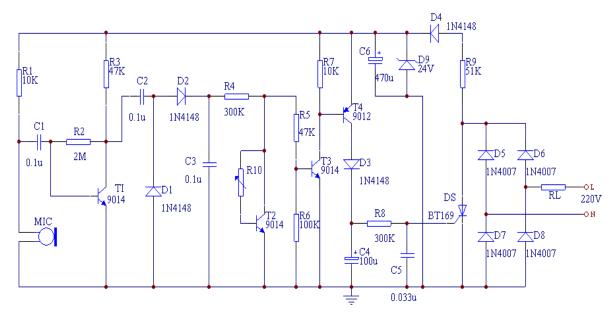

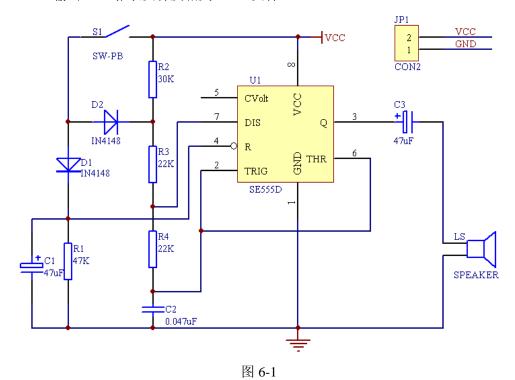

A printed circuit board (PCB), sometimes referred to as printed wiring board (PWB), is the foundation of circuit construction. Components are soldered onto the PCB, and the PCB provides the electrical connection pathways between components to form the physical circuit. Connections are made using copper tracks etched onto the various layers of the PCB. A PCB document is displayed as a set of superimposed layers, with each layer corresponding to an individual "phototool" used to fabricate the board.

In general, a PCB is derived from a schematic representation of the circuit. When a schematic is loaded into a PCB document, schematic part symbols are translated to corresponding board component footprints, and the connectivity of the schematic is preserved and displayed as connection lines in the PCB document.

# Part 1 PCB design objects

A variety of objects are available for use in designing a PCB. Keep in mind that most objects placed on a PCB document will define copper areas or voids in the physical PCB. This applies to both electrical objects, such as tracks and pads, and non-electrical objects, such as text and dimensioning. It is therefore important to keep in mind the width of the lines used to define each object, and the layer that the object is placed on.

The topics listed below give a full description of each available design object in this toolbar.

Valid Layers: All

Can be connected to a net?: Yes

An arc is essentially a curved track segment and can be used to produce curved paths during routing, or curved component or board outlines. During board routing, arcs are placed on the board when in the "Arc Corner" placement mode.

There are two methods for placing arcs on a PCB: Center or Edge placement. In each case you define a number of points on the arc in sequence by positioning the cursor and left-clicking or pressing the ENTER key. When you complete the sequence the arc will be rendered and you can begin

placing another arc. Right-click or press ESC to exit the arc placement mode.

When an arc is in focus, the following editing handles are available:

Point A marks the center of the arc. Click to "grab" the arc by its center

and move it. You can also move the arc by clicking anywhere on the arc

itself.

Click B to change the start and end points of the arc.

Click C to change the radius of the arc.

## 2. Component Footprint

Valid layers: Top or Bottom signal layers

Can be connected to a net?: No (Component pads, however, can be assigned to net)

A component footprint is the representation of a physical device on a PCB. A footprint may contain pads for connecting to the pins of a device, a physical outline of the package, device mounting features, etc.

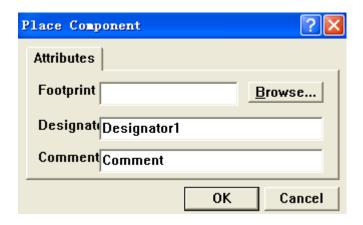

When you enter component placement mode the Place Component dialog will open.

In this dialog, type the name or browse for a component footprint from a loaded PCB library. Set the appropriate designator and any comment text, then click OK to close the dialog. You will return to the PCB document and an outline of the component will be "floating" on the cursor. Position the component and left-click or press ENTER to place it. The Place Component dialog will re-open, allowing you place another component. Press Cancel to exit component placement mode.

#### 3. Fill

A fill object places a solid rectangular block on the current PCB layer.

## **4.Track - Interactive Routing**

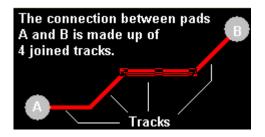

Interactive routing is the process of placing track segments. A track

is a straight solid-filled line with a defined width. Tracks are generally placed on a signal layer to form the electrical interconnection between component pads on a PCB. However, tracks are also used as general-purpose line drawing elements to create board outlines, components outlines, polygon planes, keep-out boundaries, etc.

#### 5.Pad

Pad objects are normally used to create connection pads for component pins.

In pad placement mode simply position the cursor and left-click or press ENTER to place a pad. Continue placing further pads, or right-click or press ESC to exit pad placement mode.

When a pad is in focus, the following editing handles are available:

Point A marks the center of the pad. Click here to "grab" the pad by its center and move it to a new location. You can also move a focused pad by clicking anywhere within the pad border. This will "grab" the pad at the point at which you click.

### 6.String

Can be connected to a net?: No

The string object places text on the selected PCB layer. As well as user-defined text, special strings can be used to place board or system information on the PCB, such as the layer name or a board legend, by setting the string text to be one of the special string names (see the Links section below for more information).

# Part 2 PCB design layers

A PCB is fabricated as a series of layers, including copper electrical layers, insulation layers, protective masking layers, and text and graphic overlay layers.

There are 2 types of electrical layers -signal layers, which contain the signal interconnect paths, and power planes, which are layers of unbroken copper used to distribute current to power the components.

Protel's PCB editor provides for the design of boards with up to 32 signal layers plus 16 internal plane layers. These signal and plane layers are made available in the workspace by defining the layer stack-up, which

is defined in the Layer Stack Manager dialog Design (Layer Stack Manager). As well, additional special layers, such as solder and paste masks, mechanical drawing layers, drill layers, etc, are available.

The 16 mechanical layers have a special property in that they can be added to any other layer during print or plot output generation. As well, objects placed on a special Multi layer will automatically be added to each signal layer.

Protel's PCB editor is a "layered" environment. You create your board design by placing objects on these layers. These layers are either "physical" layers, from which the fabrication information is created, or system layers, such as the Connect layer which displays the unrouted connections. Physical layers include the signal layers, internal plane layers, silkscreen, solder mask and paste mask layers.

Before you can place objects on a physical layer in your PCB document, that layer must be turned on. Once a physical layer is turned on, a Layer Tab for that layer will be displayed at the bottom of the PCB document pane in the design window.

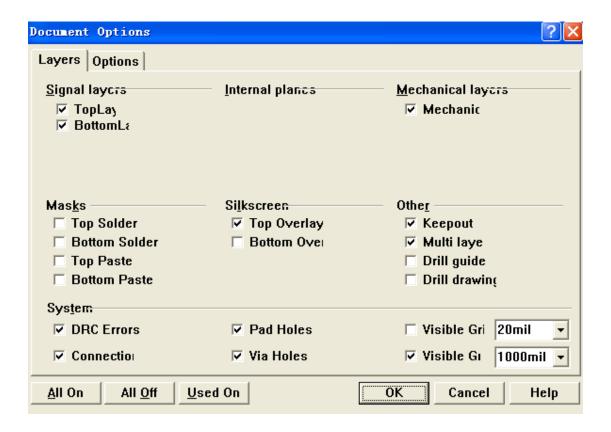

To display or hide particular layers from a PCB document select Design >Options from the menus and activate the Layers tab in the Document Options dialog [shortcut L]. For each of the layers there is a check box next to the layer name, a tick in the check box indicates that this layer is visible. Layer colors are defined in the Colors Tab of the

Preferences dialog, select Tools ?Preferences to display this dialog.

Note: Signal and plane layers will only be listed in the Document Options dialog if they have been enabled in the Layer Stack Manager dialog. Mechanical layers will only be listed if they have been enabled in the Setup Mechanical Layers dialog.

# Part 3 Defining a new PCB

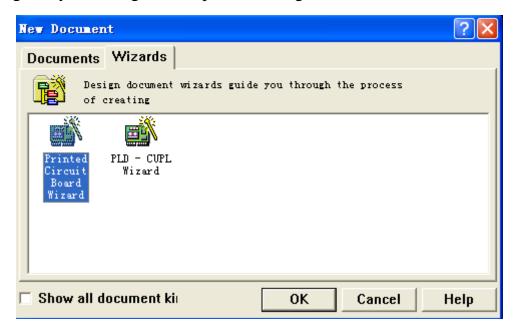

To begin the PCB design phase of a project, create a new PCB document in your design database.

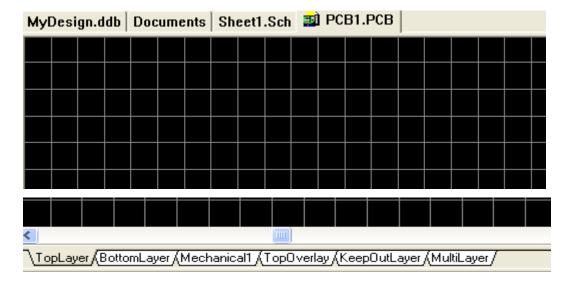

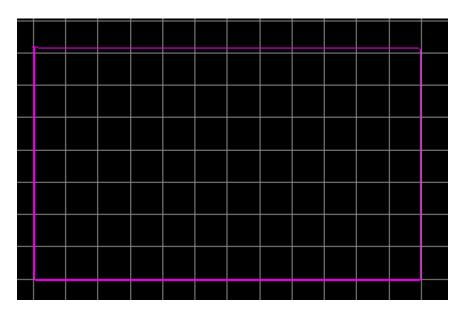

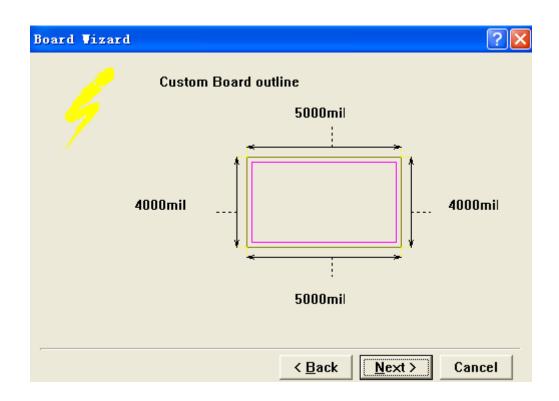

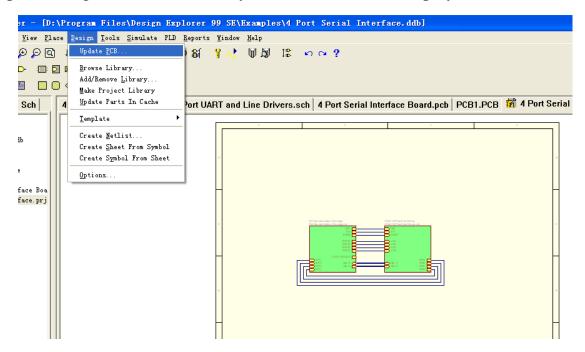

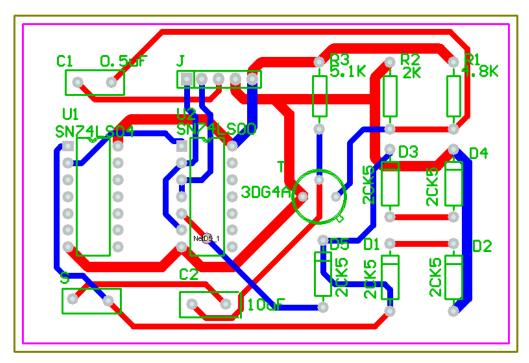

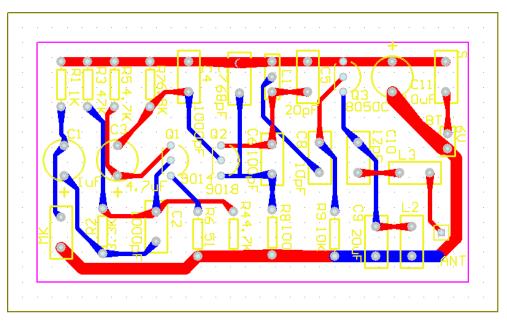

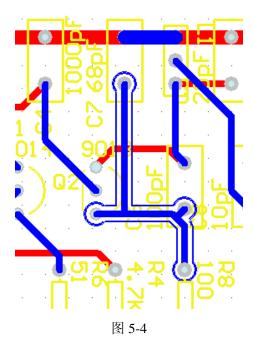

Then select OK, you will see the following board, and creat a new PCB called PCB1.PCB. In the bottom of the board, you can see the six layers .

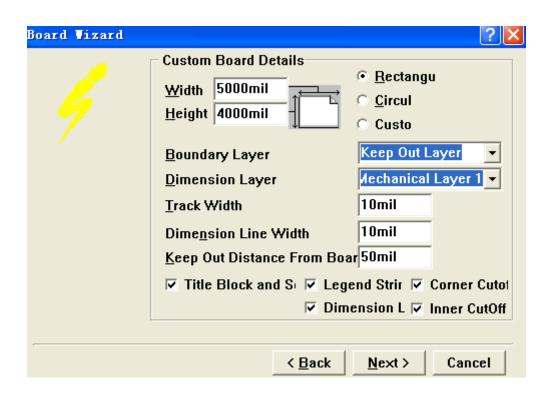

Before bringing design information from the schematic, you should first create the mechanical and electrical board outline for your board, and configure the layer stack.

The mechanical outline defines the physical shape and size of the board, and also includes items such as dimension detail, photo tool targets and other company and fabrication specific information. This information is usually placed on the four Mechanical layers.

The electrical board outline defines the routing and component placement limits of the board. This is done by defining an outline of the board on the Keep Out layer. The Keep Out layer is a special layer that allows you to define "legitimate" placement and routing areas in the PCB workspace. Generally you would define an area which is the same as the physical board outline. All signal-layer objects and routing would then be confined within this area. You could also define areas on the Keep Out layer within the board outline to act as "no go" areas for placement and routing.

The layer stack defines what signal and plane layers are available.

Part of the layer stack definition process is to define the drill-pairs.

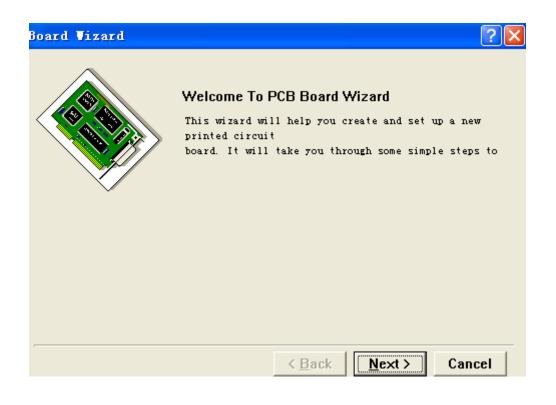

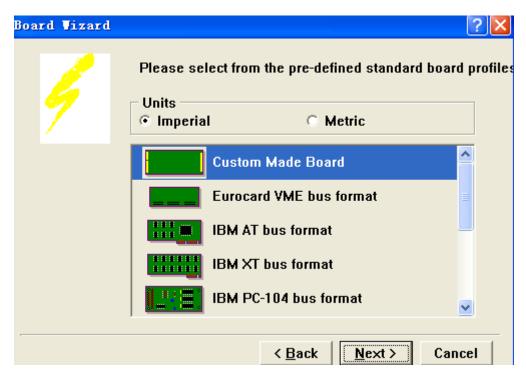

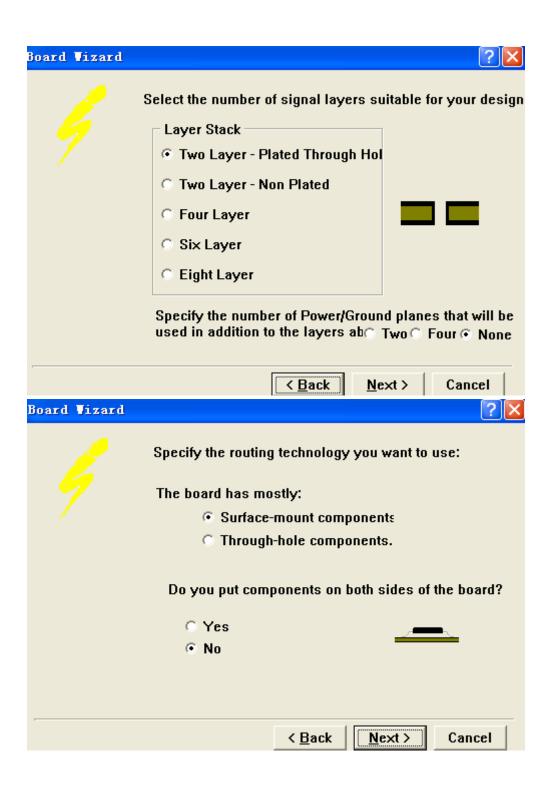

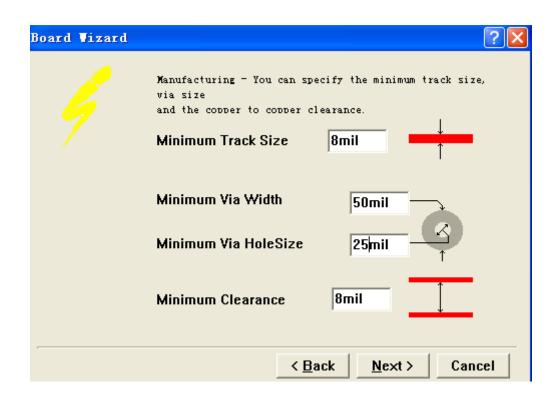

Protel 99 SE includes a powerful Board Wizard that guides you through the complete process off creating a new PCB document and board definition. The Wizard include a number of pre-defined board templates, and allows you to create your own templates.

### **Defining the PCB layer stack**

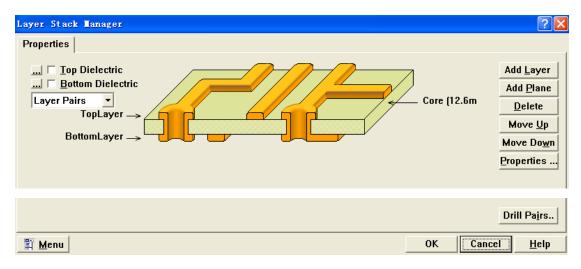

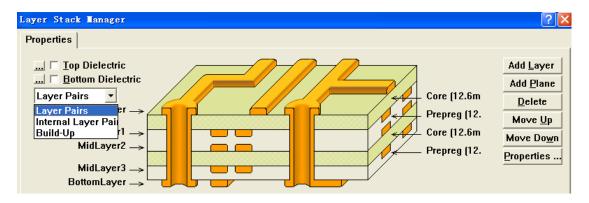

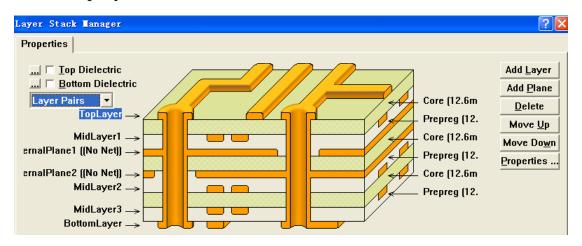

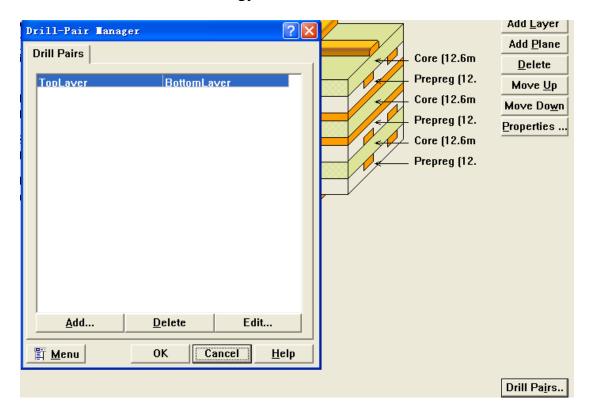

The layer stack is defined in the Layer Stack Manager dialog (Design >Layer Stack Manager)

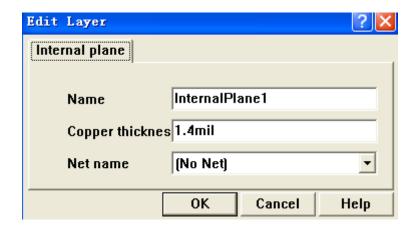

The image in the center of the dialog shows the current layer stack, the default is for a double-sided board. New layers can be added to the design by clicking on the Add Layer and Add Plane buttons. Each new layer is added below the layer that is currently selected. Double-click on a layer name to edit the properties of that layer.

The Menu button at the bottom of the dialog includes a number of pre-packed example layer stacks. Note that these example layer stacks are not fixed, you can start with one of these and easily modify it. Once the required layers have been added, use the Move Up and Move Down buttons to configure the layer stack. New layers can be added at any point in the design process.

There are a total of 32 signal layers available (top layer, bottom layer, and 30 mid-layers) and 16 plane layers. Layer visibility is controlled in the Document Options dialog (Design > Options).

### **Selecting the Layer Stack-up Style**

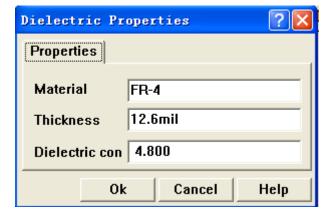

As well as the electrical layers, the stack-up includes the non-electrical insulation layers. There are typically 2 kinds of insulation used in the fabrication of a PCB, usually referred to as core and prepreg.

The stack-up style refers to the order of the insulation layers through the layer stack. Three default stack-up styles are supported **-layer-pairs**, **internal layer-pairs**, **and build up**. Changing the layer stack-up style changes the way that the core and prepreg layers are distributed through the layer stack.

Select the preferred stack-up style at the top left of the Layer Stack Manager dialog. Defining the stack-up style is required if you plan to use blind and buried vias, and for signal integrity analysis. If you are planning to use blind and buried vias you must consult with your PCB manufacturer to ensure that that they can fabricate the design, and that the correct stack-up style is selected.

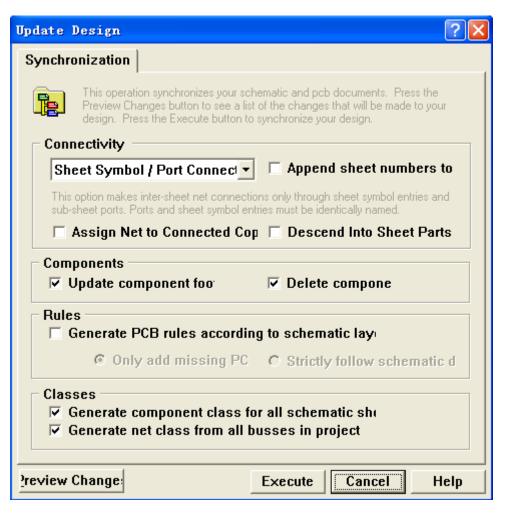

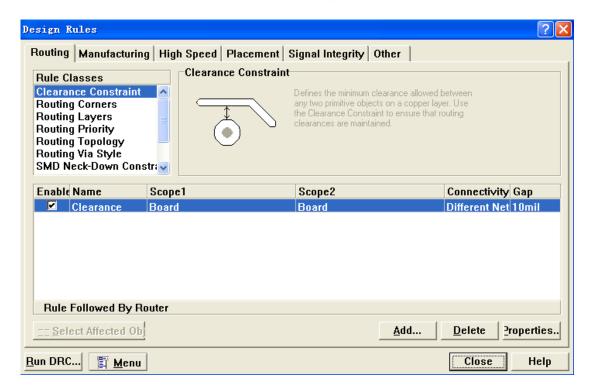

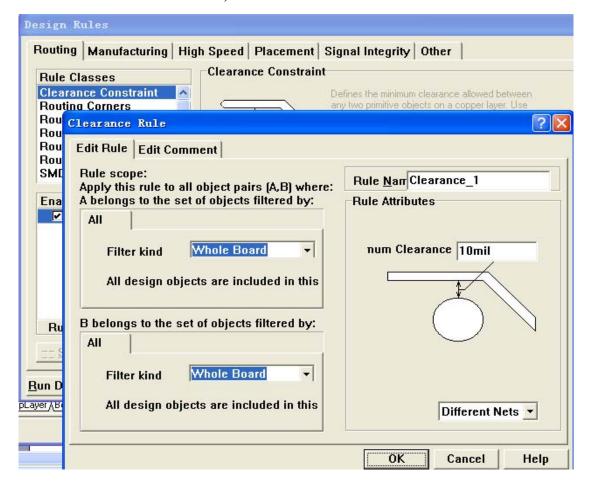

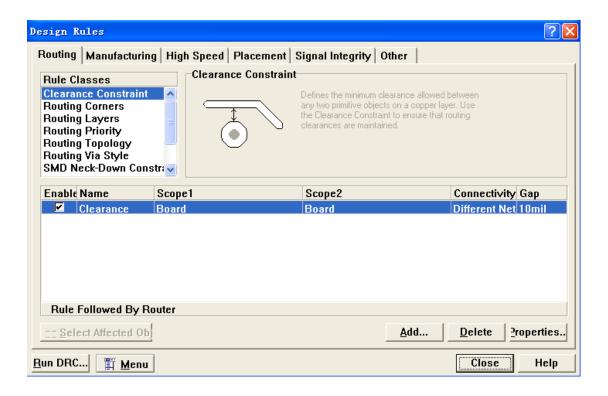

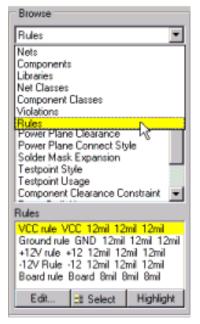

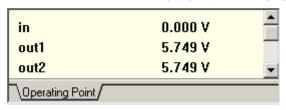

# **Defining the layer properties**